**AN83**

## **Application Note**

### Crystal LAN™ CS8900A ETHERNET CONTROLLER TECHNICAL REFERENCE MANUAL

By Deva Bodas Revised by James Ayres

#### TABLE OF CONTENTS

| SCHEMATIC CHECKLIST                                            |    |

|----------------------------------------------------------------|----|

| SOFTWARE CHECKLIST                                             | .5 |

| INTRODUCTION TO CS8900A TECHNICAL REFERENCE MANUAL             | .6 |

| HARDWARE DESIGN                                                | .7 |

| CS8900A: CONNECTING TO NON-ISA BUS SYSTEMS                     | .7 |

| The CS8900A Architecture                                       | .7 |

| ISA Bus                                                        | .8 |

| CS8900A in I/O Mode                                            | .8 |

| CS8900A in Memory Mode                                         | .8 |

| DMA Interface of the CS8900A                                   | .8 |

| Selection of I/O, Memory and DMA Modes                         | .9 |

| Design Example: CS8900A Interface to MC68302                   | .9 |

| Address Generation                                             | .9 |

| Read and Write Signals                                         | 10 |

| SBHE Signal                                                    |    |

| Other Control Signals                                          |    |

| Status Signals from CS8900A                                    |    |

| Databus (SD[0:15]) Connection                                  | 11 |

| Checklist for Signal Connections to the CS8900A                |    |

| EEPROM Optional                                                | 11 |

| Design Example: CS8900A Interface to Cirrus Logic CL-PS7111    | 12 |

| Design Example: CS8900A Interface to Hitachi SH3               | 12 |

| Summary                                                        | 12 |

| ETHERNET HARDWARE DESIGN FOR EMBEDDED SYSTEMS AND MOTHERBOARDS |    |

| General Description                                            |    |

| Board Design Considerations                                    |    |

| Crystal Oscillator                                             |    |

| ISA Bus Interface                                              |    |

| External Decode Logic                                          |    |

| EEPROM                                                         |    |

|                                                                |    |

| 10BASE-T Interface                                             |    |

|                                                                |    |

| Logic Schematics<br>Component Placement and Signal Routing     |    |

| Bill of Material                                               |    |

|                                                                | źυ |

#### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Crystal LAN, StreamTransfer, PacketPage, and SMART Analog are trademarks of Cirrus Logic.

Ethernet is a registered trademark of Xerox Corp.. Artisoft and LANtastic are registered trademarks of Artisoft, Inc.. Banyan and VINES are registered trademarks of Banyan Systems.. Digital and PATHWORKS are registered trademarks of Digital Equipment Corporation.. Intel is a registered trademark of Intel Corporation.. LAN Server and IBM are registered trademarks of International Business Machines Corp.. Microsoft, LAN Manager, Windows 95, Windows for Workgroups, and Windows NT are registered trademarks of Microsoft.. Novell and Netware are registered trademarks of Novell, Inc.. SCO is a registered trademark of Santa Cruz Organization, Inc.. UNIX is a registered trademark of AT&T Technologies, Inc.

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, nor for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or other wise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

| LOW COST ETHERNET COMBO CARD REFERENCE DESIGN: CRD8900                     |    |

|----------------------------------------------------------------------------|----|

| General Description                                                        | 21 |

| Board Design                                                               |    |

| Crystal Oscillator                                                         |    |

| ISA Bus Interface                                                          |    |

| External Decode Logic                                                      | 21 |

| EEPROM                                                                     |    |

| Socket for Optional Boot PROM                                              |    |

| LEDs                                                                       |    |

| 10BASE-T Interface                                                         |    |

| AUI Interface                                                              |    |

| 10BASE-2 Interface                                                         |    |

| Logic Schematics                                                           | 27 |

| Component Placement and Routing of Signals                                 | 27 |

| Bill of Material                                                           | 27 |

| Addressing the CS8900A: I/O Mode, Memory Mode                              | 27 |

| I/O Mode                                                                   |    |

| Memory Mode                                                                |    |

| Lower Memory Mode                                                          |    |

| Extended Memory Mode                                                       | 31 |

| Layout Considerations for the CS8900A                                      | 35 |

| General Guidelines                                                         |    |

| Power Supply Connections                                                   | 35 |

| Two Layered Printed Circuit Board (PCB)                                    | 35 |

| Multi-layered Printed Circuit Board                                        |    |

| Routing of the Digital Signals                                             | 35 |

| Routing of the Analog Signals                                              | 35 |

|                                                                            |    |

|                                                                            |    |

| Serial EEPROM                                                              |    |

| Reset Configuration Block                                                  |    |

| Driver Configuration Information                                           | 47 |

| Format of Driver Configuration Block                                       |    |

| IEEE Physical Address                                                      |    |

| ISA Configuration Flags                                                    |    |

| PacketPage Memory Base                                                     |    |

| Boot PROM Memory Base                                                      |    |

| Boot PROM Mask                                                             |    |

| Transmission Control                                                       |    |

| Adapter Configuration Word                                                 |    |

| EEPROM Revision                                                            |    |

| Manufacturing Date                                                         |    |

| IEEE Physical Address (Copy)                                               |    |

| 16-bit Checksum                                                            |    |

| EISA ID                                                                    |    |

| Serial Number                                                              |    |

| Serial ID Checksum                                                         |    |

| Maintaining EEPROM Information                                             |    |

| Embedded Designs                                                           |    |

| BIOS-Based Design Considerations                                           |    |

| Driver Interface with BIOS-Based Configuration                             |    |

| OBTAINING IEEE ADDRESSES<br>DEVICE DRIVERS AND SETUP/INSTALLATION SOFTWARE | 55 |

|                                                                            |    |

| DOS Setup and Installation Utility<br>Installation Procedure               | 50 |

| CONTACTING CUSTOMER SUPPORT AT CIRRUS                                      | 50 |

| CONTACTING CUSTOMER SUPPORT AT CIRRUS                                      |    |

| Cirrus web oile                                                            | 57 |

#### SCHEMATIC CHECKLIST

Before getting into the meat of the technical reference manual here is a schematic checklist. It's presented here, at the beginning, to help the hardware designer implement the design quickly and easily.

- No caps across the crystal. The CS8900A implements these internally.

- 4.99K 1% resistor between pin 93 and pin 94. A common mistake is the resistor is connected to Vcc instead of ground.

- RESET is active high, not active low.

- Check addressing.

- On non-ISA systems, if the processor is Big Endian, it may be beneficial to byte swap the data lines to minimize byte swapping in software.

- SBHE (16 bit mode) -- must be low on IO or Mem address. And it must toggle at least once to put the CS8900 in 16 bit mode.

- IO and Memory Accesses: SBHE, AEN, etc. must be stable for 10ns (read) and 20ns (write) before access.

- IOCHRDY Generally not connected in non-ISA bus.

- CHIPSEL (active low). Tie to ground if not using ELCS.

- Make sure interrupt line is active high. It is best to put a pull down (10K) on INT line since selected IRQ line is tristated during software initiated reset.

- ELCS should be pulled to ground if not used.

- EEDataIn should be pulled to ground if not used.

- 10Base-T circuit -- no caps on TX lines between isolation transformer and 10 Base-T connector.

- 10Base-T circuit -- no center tap caps on isolation transformer and 10 Base-T connector. Good to have pads, don't populate except for

EMI problems.

- Isolation transformer -- start with one that does not have a common mode choke. If there are EMI considerations, then use one with common mode choke. The pin outs are the same. For 3.3V operation, use a transformer with 1:2.5 turns ration on TX and 1:1 on RX like the Halo TG41-2006N.

- For EMI problems, 1) add choke, 2) add center tap caps on isolation transformer

- If using a shielded RJ45 connector, make sure the shield pins are connected to chassis ground.

- AEN connected to ground if not using DMA.

- AEN can be used as an active low chip select if not using DMA.

- AUI Interface -- use a 1AMP fuse. MAU can use .5amps even better use a thermistor ("poly switch"). Also, use a diode so can't back-drive from an externally powered MAU. Use a Halo TnT integrated module to simplify 10Base2 interface.

- TX series termination resistors are R: 24.3 Ohm

1% (8 Ohm 1% for 3.3V)

- RX shunt termination resistor is 100 Ohm

- Put a 68pF shunt across TX on primary side (560pF for 3.3V)

- Don't use split analog/digital power and ground planes.

- Void ground/power plane from transformer to RJ45

- Put .1uF cap on each supply pin very close to CS8900

The schematic checklist and the example connection diagrams to the Hitachi SH3, Cirrus Logic CL-PS7111 and the Motorola MC68302 microprocessors should make clear the necessary the hardware connections for a wide variety of situations.

#### SOFTWARE CHECKLIST

- When servicing the interrupt always read the Interrupt Status Queue (ISQ) first. Process that individual event before reading the ISQ again.

- Having read an ISQ event indicating a valid recieve frame, never read the ISQ again before either 1) reading in the entire current receive frame or 2) issuing an explicit skip command. Either of these actions will correctly clear that frame from the CS8900A's internal memory.

- Always continue reading and processing ISQ events until reading a 0x0000 from the ISQ.

- After a software or hardware reset, always wait until the SelfStatus register, bit 7 (INITD) is set before reading or writing any other registers.

- Allow only one transmit in progress at any given time. Since the chip dynamically allocates memory between transmit and recieve frames, it is possible to fill the internal buffers with transmit frames. This would prevent reception.

- Don't reinvent the wheel. Port one of the sample drivers, if there isn't a driver for your operating system. You can find sample drivers at http://www.cirrus.com/drivers/ethernet/.

#### INTRODUCTION TO CS8900A TECHNICAL REFERENCE MANUAL

This Technical Reference Manual provides the information which will be helpful in designing a board using the CS8900A, programming the associated EEPROM, and installing and running the CS8900A device drivers. It is expected that the user of this technical reference manual will have a general knowledge of hardware design, Ethernet, the ISA bus, and networking software. Recommended sources of background information are:

<u>ISA System Architecture</u> by Shanley and Anderson, Mindshare Press, 1992, ISBN 1-881609-05-7

Ethernet, Building a Communication Infrastructure, by Hegering and Lapple, Addison-Wesley, 1993, ISBN 0-201-62405-2

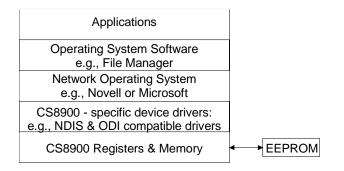

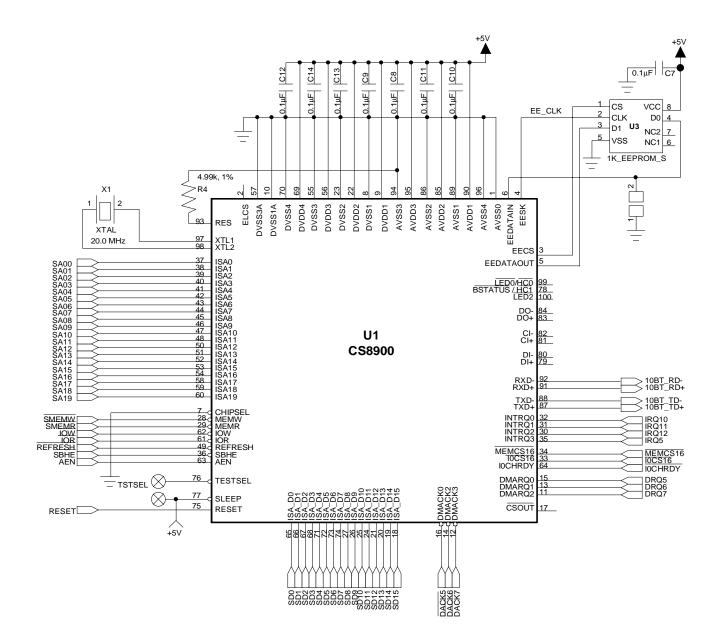

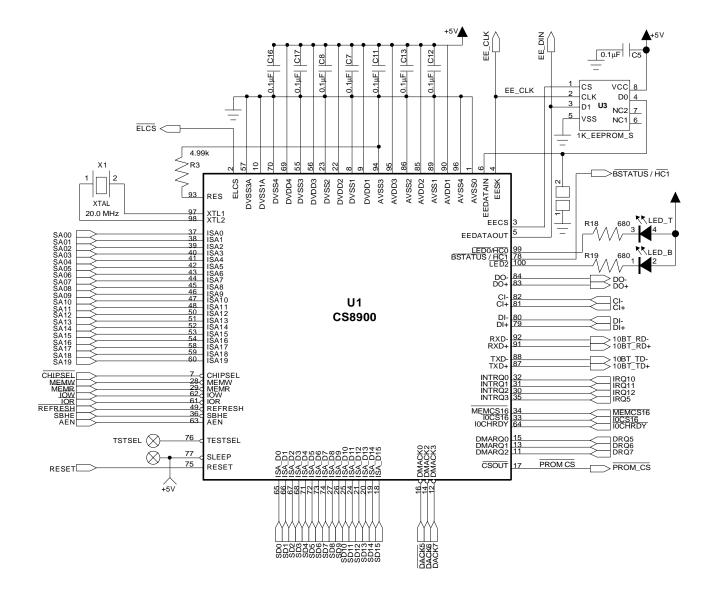

Netware Training Guide: Networking Technologies, by Debra Niedenmiller-Chaffis, New Riders Publishing, ISBN 1-56205-363-9 As shown in the Figure 1, the CS8900A requires a minimum number of external components. The EEPROM stores configuration information such as interrupt number, DMA channel, I-O base address, memory base address, and IEEE Individual Address. The EEPROM can be eliminated on a PC motherboard if that information in stored in the system CMOS. Note also that the Boot PROM is only needed for diskless workstations that boot DOS at system power up, over the network. Also, the LEDs are optional.

The hardware design considerations for both motherboards and adapter cards are discussed in "HARDWARE DESIGN" on page 7. The EE-PROM programming considerations are described in "JUMPERLESS DESIGN" on page 45.

Cirrus provides a complete set of device drivers, as discussed in "DEVICE DRIVERS AND SET-UP/INSTALLATION SOFTWARE" on page 56. The drivers reside between the networking operating system (NOS) and the CS8900A. On the CS8900A side, the drivers understand how to pro-

Figure 1. Hardware Application Summary

gram and read the CS8900A control and status registers, and how to transfer user data between the CS8900A and the PC main memory via the ISA bus. On the NOS side, the drivers provide the standardized services and functions required by the NOS, and hide all details of the CS8900A hardware from the NOS. The EEPROM device programs the CS8900A whenever the a hardware reset occurs, and call also store state/configuration information for the driver.

Cirrus's Software Driver (**Crystal LAN™**) Distribution Policy is as follows. The CS8900A developer kit contains a single-user copy of object code which is available only for internal testing and evaluation purposes. This object code may not be distributed without first signing a LICENSE FOR DISTRIBU-TION OF EXECUTABLE SOFTWARE, which may be obtained by contacting your sales representative. The LICENSE FOR DISTRIBUTION OF EXECUTABLE SOFTWARE gives you unlimited, royalty-free rights to distribute Cirrus-provided object code.

#### HARDWARE DESIGN

This section give design guidance for both embedded and adapter card designs, including recommendations for dealing with the upper ISA address lines (LA[20:23]), choosing transformers, and laying out the board.

Figure 2. Software Application Summary

#### CS8900A: CONNECTING TO NON-ISA BUS SYSTEMS

The CS8900A includes a direct interface to the ISA bus. At the same time, the CS8900A offers a compact, efficient, and cost-effective, full-duplex Ethernet solution for non-ISA architectures. The purpose of this section is to illustrate how to interface the CS8900A to non-Intel and non ISA systems. Design examples include the MC68302, Cirrus Logic CL-PS7111 ARM and Hitachi SH3.

#### The CS8900A Architecture

The CS8900A is a highly integrated Ethernet controller chip. It includes the digital logic, RAM and analog circuitry required for an Ethernet interface. This high level of integration allows a product designer to design an Ethernet interface in 1.5 square inches of space on a printed circuit board. The CS8900A has a powerful memory manager that dynamically allocates the on-chip memory between transmit and receive functions. The on-chip memory manager performs functions in hardware that are many times done by software. This reduces loading on the CPU and on the bus connected to the CS8900A. In fact, for 10 Megabit Ethernet, the CS8900A is the highest throughput solution in the market.

The integration of the analog transmit waveform filtering makes it easier to design a board that will pass EMC testing. When the analog filters are external, the PCB traces have fast edge digital waveforms coming out of the IC's 10BASE-T transmitter. The presence of high frequency energy in the fast edges causes major problem during EMC tests, such as FCC Part 15 class (B) or CISPR class (B). The 10BASE-T signals driven out of the CS8900A are internally filtered with a 5<sup>th</sup> order Butterworth filter and the signals lack fast edges. Lack of high frequency signals makes it straight forward to design a card that meets FCC class (B) or even CISPR class (B) requirements.

#### ISA Bus

An ISA bus is a simple, asynchronous bus that can easily be made to interface to most synchronous or asynchronous buses. An ISA bus has separate address and data lines as well as separate control lines for read and write. ISA supports IO address space of 64K bytes and Memory address space 32 Mega bytes.

#### CS8900A in I/O Mode

When the CS8900A is used in an IO mode, it responds in the IO address space of the ISA. The CS8900A responds to an IO access when

- Either of the bus IO command lines (IOR or IOW) is active,

- The address on bus signals SA[0:15] matches the address in the CS8900A IO base address register, and

- Bus signals AEN, REFRESH, TEST, SLEEP and RESET are inactive.

All other control signals are ignored for the IO operation.

In an IO mode, the CS8900A uses 16 bytes of IO address space. The address map for this mode is described in Table 4.5 in the CS8900A datasheet.

#### CS8900A in Memory Mode

When the CS8900A is used in memory mode, the CS8900A responds in the memory address space of the ISA bus. The CS8900A responds to a memory mode access when

- The CHIPSEL pin is active,

- Either of the bus memory command lines (MEMR or MEMW) is active,

- Both of the IO command lines (IOR and IOW) are inactive,

- the address on bus signals SA[0:19] matches the address in the CS8900A's Memory Base address register,

- MemoryE (Bit A) in the CS8900A's BusCTL (Register 17) is active and,

- Bus signals AEN, REFRESH, TEST, SLEEP and RESET are inactive.

In memory mode, all the internal registers of the CS8900A can be accessed directly via memory reads/writes. Please refer to the CS8900A datasheet for the memory address map.

#### DMA Interface of the CS8900A

The CS8900A can interface to an external 16-bit DMA channel for receive operations. A DMAmode receive operation can be selected by setting either RxDMAOnly (bit 9) or AutoRxDMA (bit 10) in the CS8900A's RxCFG (Register 3) register. The CS8900A will request services of an external DMA after a receive frame is accepted by the CS8900A, completely received and stored in on chip RAM of the CS8900A. The CS8900A generates a request for DMA access (DRQx) signal when it has at least one receive frame that can be transferred to the system memory. The external DMA channel should assert DMACK signal when it is ready to transfer data. The DMA controller generates address for the system memory and asserts the AEN signal. When  $\overline{\text{DMACK}}$  and AEN signals are asserted, the CS8900A provides 16 bits of frame data for every pulse of the  $\overline{IOR}$  signal. Notice that the CS8900A ignores address on the SA address lines for this operation. In this way the CS8900A supports "direct mode" of operation of DMA. In direct mode, the external DMA controller generates addresses for the system RAM, and generates the appropriate control signals for the RAM and IO device. The data moves directly from the IO device to the RAM. In the case of the CS8900A, the DMA controller generates a write signal for RAM and a read signal for the CS8900A. The data flows directly from the CS8900A to the system RAM. The direct mode of DMA operation is 100% more efficient than typical read-followed-by-write DMA operation.

The length of time that the CS8900A holds the DRQ signal active depends upon the DMABurst (bit B) bit of the BusCTL (Register 17) register. If the DMABurst is clear, the DRQ remains active as

long as the CS8900A contains frames completely received. If 'n' words are to be transferred from the CS8900A to the system RAM, the DRQ signal remains active until the  $(n-1)^{th}$  word is transferred. If the DMABurst is set, then the CS8900A deasserts DRQ signal for 1.3 µs after every 28 µs. This option is provided so that in a system where multiple DMA channels are operational, the DMA used for the CS8900A will not take over the system bus for long periods of time.

#### Selection of I/O, Memory and DMA Modes

The CS8900A always responds to all IO-mode requests. After any reset, the CS8900A responds to default IO base address of 0300h. However, this default IO address can be changed by writing a different base address into a EEPROM connected to the CS8900A. After any reset, the CS8900A reads the contents of the EEPROM. If the EEPROM is found valid, then the information in the EEPROM is used by the CS8900A to program its internal registers.

Memory mode in the CS8900A can be enabled by programming a proper base-address value in the Memory Base Address register and setting the MemoryE bit. Enabling of the memory mode can be done by software or through an EEPROM connected to the CS8900A.

In an IO mode, the CS8900A takes the minimum space (16 bytes) in the system address space. For systems where the address space limited, the IO mode is a proper choice.

The memory mode is the most direct and efficient mode of operation for the CS8900A. In the memory mode the CS8900A occupies 4K of the address space. The software can access any of the internal registers of the CS8900A directly. This reduces accesses to the CS8900A by half when accessing registers.

In a system design, even if CS8900A is used in the memory mode, the designer should make provi-

sions for accessing the CS8900A in the IO mode. This dual-mode access has two advantages.

- 1) If an EEPROM is not used in the Ethernet design, the application can address the CS8900A in IO mode (0300h) in order to enable memory mode.

- When the EEPROM is used, the EEPROM is usually blank when a board is manufactured. The CS8900A must be accessed in IO mode in order to program the EEPROM.

Use of DMA for receive is efficient in a multi-tasking environment where the CPU could be busy servicing several higher priority tasks before it can service receive frames off the Ethernet wire.

# Design Example: CS8900A Interface to MC68302

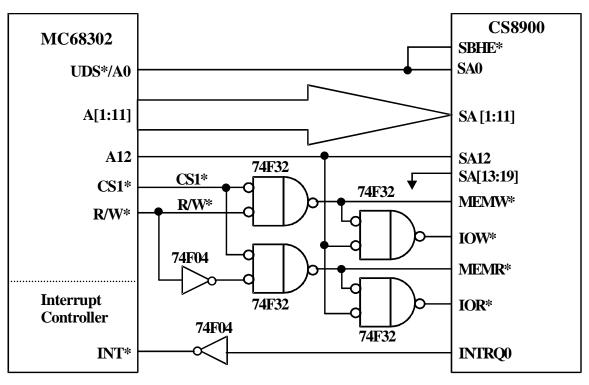

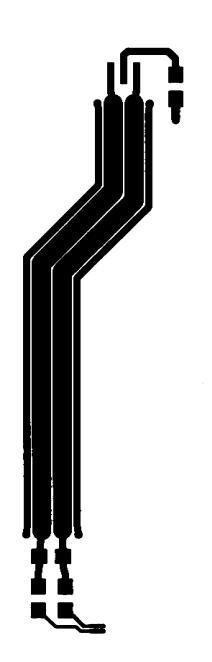

In this example the CS8900A is connected to Motorola micro-controller MC68302. Please refer to Figure 3 to check the connection of control signals between CS8900A and Motorola's micro-controller MC68302.

#### Address Generation

The MC68302 has address decode generation logic internal to the micro-controller. It generates chip select signals such as  $\overline{CS1}$ . In this example the  $\overline{CS1}$ is used to access the CS8900A in IO as well as in Memory mode. The behavior of the  $\overline{CS1}$  signal from the MC68302 is governed by values programmed in the CS1 base address register and the CS1 option register. For example, if the CS1 base address register is programmed as 3A01h, the  $\overline{CS1}$ will have a base address of D00xxxh. The CS1 operation register controls the address range, number of wait states (to be inserted automatically), etc. It is recommended that the CS8900A be assigned 8K of address space (0D00000h-0D01FFFh). Memory mode of the CS8900A is enabled with the memory base address register with a value 001000h. The address line A12 separates IO address space and memory address space. When A12 is low, the

CS8900A is accessed in an IO mode and when A12 is high, the CS8900A is accessed in memory mode. When the MC68302 generates address 0D00300h, the address seen by the CS8900A will be 00300h with one of the IO commands (IOR or IOW) active. Similarly when the MC68302 generates address 0D01400h, the address seen by the CS8900A will be 01400h with one of its memory commands (MEMR or MEMW) active. For a MC68302, you can also specify the number of wait states that should be inserted automatically when address space assigned to CS1 is accessed. The number of wait states used depends upon the clock input to the MC68302. Please do a complete timing analysis before defining wait states.

#### **Read and Write Signals**

The combination of OR gates and an inverter shown in Figure 3, generates IO commands ( $\overline{IOR}$ ,  $\overline{IOW}$ ) as well as memory commands ( $\overline{MEMR}$ ,  $\overline{MEMW}$ ) for the CS8900A. Since the  $\overline{CS1}$  gates

these signals, the IO or memory commands are not generated unless the address on the address bus is stable. Further, for an access in memory mode, an IO command is not active.

#### **SBHE** Signal

The CS8900A is a 16 bit device and it should be used as a 16 bit device. However, after a hardware or software reset, the CS8900A behaves as an 8 bit device. Any transition on pin  $\overline{\text{SBHE}}$  places the CS8900A into 16-bit mode. Further, for a 16-bit access, the  $\overline{\text{SBHE}}$  pin of the CS8900A must be low. In the design example, the CPU address line A0 is connected to  $\overline{\text{SBHE}}$ . Before any access to the CS8900A, the design must guarantee one transition on  $\overline{\text{SBHE}}$  pin.

#### **Other Control Signals**

All other control signals can be tied HIGH or LOW. The signal  $\overline{\text{REFRESH}}$ ,  $\overline{\text{TEST}}$ ,  $\overline{\text{SLEEP}}$ , AEN should be tied inactive.

Figure 3. Connection of CS8900A to MC68302

#### Status Signals from CS8900A

There are several status signals that are output from the CS8900A, such as IOCHRDY,  $\overline{IOCS16}$ ,  $\overline{MCS16}$ , etc. In the most embedded designs, they are not needed. Those pins from the CS8900A should be left open.

#### Databus (SD[0:15]) Connection

All the internal registers of the CS8900A are 16 bit wide. For all the registers, bit F of the register is access via SD15 and bit 0 of register is accessed via SD0.

To be compatible with byte ordering with ISA bus, the CS8900A provides the bytes received from the Ethernet wire in the following fashion. Assume that the data received from the Ethernet wire is 01. 02, 03, 04, 05, ... where the 01 is the first byte, 02 is the second byte and so on. When the CS8900A transfers that data to the host CPU, the data words are read from the CS8900A as 0201, 0403, etc. For certain microprocessor systems, the designer may prefer to read the data as 0102, 0304, etc. In such a case, the databus connections to the CS8900A can be altered by connecting the CPU databus D[0:7] to the SD[8:15] pins of the CS8900A and the CPU databus D[8:15] to the SD[0:7] pins of the CS8900A. In such a case, make sure that all the register and bit definitions in the CS8900A are also byte swapped. Information that is normally appears at bits [0:7] will now appear on bits [8:15], and information that usually appears on bits [8:15] will now appear on bits [0:7].

## Checklist for Signal Connections to the CS8900A

Please refer to the datasheet for the CS8900A for the pin assignment and pin descriptions of various signals discussed in this section.

Clock: There are two options for the clock connection to the CS8900A. You may connect a 20.000 MHz crystal between XTL1 (pin 97) and XTL2 (pin 98) pins of the CS8900A. Or, if there a 20 MHz clock available in the system, it can be connected to the XTL1 (pin 97) pin of the CS8900A. It is important that this clock be TTL or CMOS with 40/60 duty cycle and  $\pm 50$  ppm accuracy.

**SBHE** signal: It is recommended that the CS8900A be used in 16-bit mode. After a hardware or software reset, the CS8900A comes up as an 8-bit device. A transition on  $\overline{\text{SBHE}}$  signal (pin 36) makes the CS8900A function as a 16-bit device. After this transition, the  $\overline{\text{SBHE}}$  can be kept low. For a 16-bit access of the CS8900A, the SBHE and address line SA0 (pin 37) must be low. Un-aligned word accesses to the CS8900A are not supported. In a system, the SBHE line can be connected to address line SA0. In such a case, after a hardware or software reset, do a dummy read from an odd address to provide transition on the SBHE line. For memory mode, there is one more alternative for the **SBHE** connection. For a memory mode operation, if a CHIPSEL pin is controlled by an external chip select, the CHIPSEL can be connected to the  $\overline{\text{SBHE}}$ . In this case, after a hardware and software reset, do a dummy access to the CS8900A and ignore data.

#### **EEPROM Optional**

The CS8900A has an interface for a serial EE-PROM. Most of the networking applications use this EEPROM to store IEEE MAC (Media Access Control) address. Since the CS8900A supports 1 or 2 Kbits of EEPROM, the EEPROM is also used to store information such as hardware configuration, software driver configuration, etc. Any location in the EEPROM can be read or written through the CS8900A.

You will require EEPROM if the IO address for the CS8900A has to be other then 0300h, or the only mode supported by the CS8900A is memory mode. For all other cases an EEPROM is optional. However, most of the software drivers supplied by Cirrus assume that there is an EEPROM connected to the CS8900A or driver configuration data is stored

in BIOS. If the designer intends to use Cirrus supplied drivers and does not use an EEPROM or store driver configuration data in BIOS, then Cirrus supplied drivers must be modified by the designer.

We recommend that the system store the individual IEEE MAC address in a non-volatile memory somewhere in the system, and that the end-user of the system not be allowed to create an arbitrary address. In a LAN, the existence of network nodes that use the same MAC address will cause severe network problems including destruction of data and failure of various network nodes.

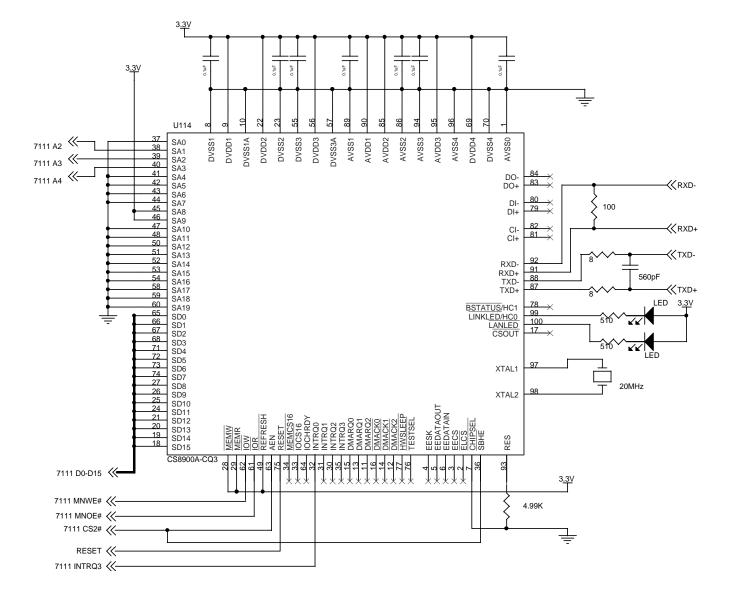

#### Design Example: CS8900A Interface to Cirrus Logic CL-PS7111

This design is similar to the MC68302 except that only the I/O mode data access is supported. This completely elimiates glue logic. See Figure 4. The highlights of the design are:

- CS8900A I/O space mapped into 7111 memory

- 3 address lines offset by 1 due to 7111's 32 bit data accesses

- A8 and A9 tied high

- AEN used as active low chip select

- SBHE tied to 7111 chip select

- Only 16 bit accesses

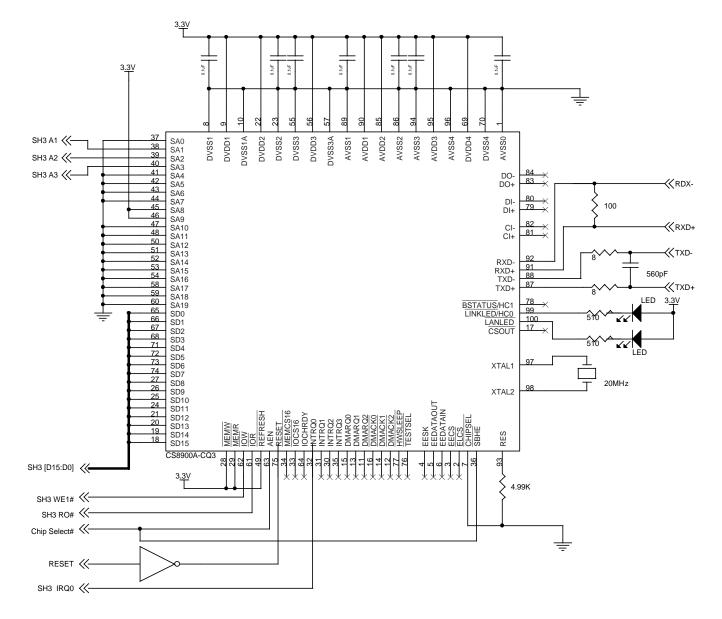

# **Design Example: CS8900A Interface to Hitachi SH3**

This design is almost identical to the CL-PS7111 connection diagram. It uses I/O mode only, eliminating glue logic. See Figure 5. The highlights of the design are:

- CS8900A I/O space mapped into SH3 memory

- 3 address lines A0 is tied to ground.

- A8 and A9 tied high

- AEN used as active low chip select

- SBHE tied to SH3 chip select

- Inverter on the IRQ line.

- Only 16 bit accesses

#### Summary

The CS8900A can be interfaced to most non-ISA system with very minimum or no external logic. This allows a low cost, small size and very efficient Ethernet solution for non-ISA systems. Cirrus Logic will provide support for non-ISA designs, including logic schematic review and layout review for design engineers. Those reviews help prevent logic errors, and help to minimize EMI emissions.

Figure 4. CS8900A Interface to Cirrus Logic CL-PS7111

Figure 5. CS8900A Interface to Hitachi SH3

#### ETHERNET HARDWARE DESIGN FOR EMBEDDED SYSTEMS AND MOTHERBOARDS

This section describes the hardware design of a four-layer, 10BASE-T solution intended for use on PC motherboards, or in other embedded applications. The goal of this design is minimal board space and minimal material cost. Therefore, a number of features (BootPROM, AUI, 10BASE-2) are not supported in this particular PCB design. An example of this circuit is included in this technical reference manual, and is implemented in an ISA form factor. This same circuit can be implemented directly on the processor PCB.

#### **General Description**

The small footprint, high performance and low cost of the CS8900A Ethernet solution, makes the CS8900A an ideal choice for embedded systems like personal computer (PC) mother boards. The very high level of integration in the CS8900A results in a very low component count Ethernet design. This makes it possible to have a complete solution fit in an area of 1.5 square inches.

#### **Board Design Considerations**

#### Crystal Oscillator

The CS8900A, in this reference design, uses a 20.000 MHz crystal oscillator. The CS8900A has internal loading capacitance of 18pF on the XTAL1 and XTAL2 pins. No external loading capacitors are needed. Please note that the crystal must be placed very close to XTL1 and XTL2 pins of the CS8900A.

This crystal oscillator can be eliminated if accurate clock signal (20.00 MHz  $\pm 0.01\%$  and 45-55 duty cycle) available in the system.

#### ISA Bus Interface

The CS8900A has a direct ISA bus interface. Note that the ISA bus interface is simple enough to allow

the CS8900A to interface with variety of microprocessors directly or with the help of simple programmable logic like a PAL or a GAL.

This reference design uses the ISA adapter card form factor. All the ISA bus connections from the CS8900A are directly routed to the ISA connector. The pin-out of the CS8900A is such that if the CS8900A is placed as shown in Figures 6 and 7, there will be almost no cross-over of the ISA signals.

#### External Decode Logic

The CS8900A can be accessed in I/O mode or memory mode. For this reference design, in memory mode the CS8900A is in the conventional or upper memory of the PC. That is, it resides in the lower 1 Mega bytes of address space.

To use the CS8900A in extended memory address space requires an external address decoder. This decoder decodes upper 4 bits (LA[20:23]) of 24 bit ISA address lines. In many embedded microprocessors such decodes are available though the microprocessors itself.

Please refer to "Extended Memory Mode" on page 31 for further information.

#### EEPROM

A 64 word (64 X16 bit) EEPROM (location U3) is used in the reference design to interface with the CS8900A. This EEPROM holds the IEEE assigned Ethernet MAC (physical) address for theboard (see "Obtaining IEEE Addresses" on page 55). The EEPROM also holds other configuration information for the CS8900A. The last few bytes of the EEPROM are used to store information about the hardware configuration and software requirements.

In an embedded system, such as a PC, the system CMOS RAM or any other non-volatile memory can be used to store the IEEE address and Ethernet configuration information. In such a case an EE-

# AN83REV2

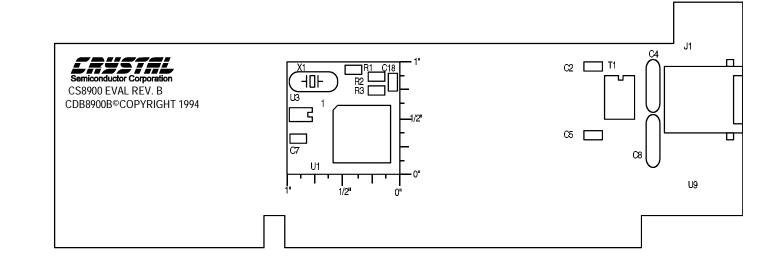

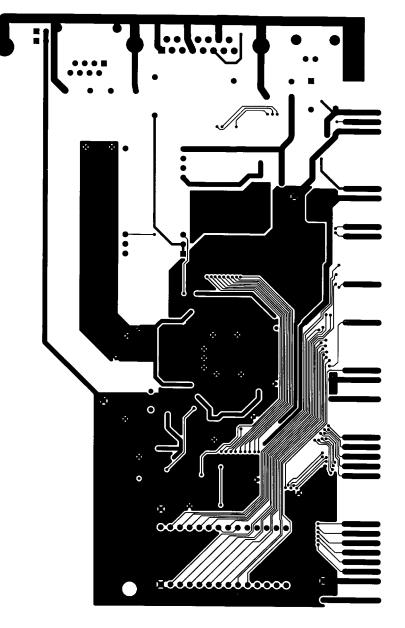

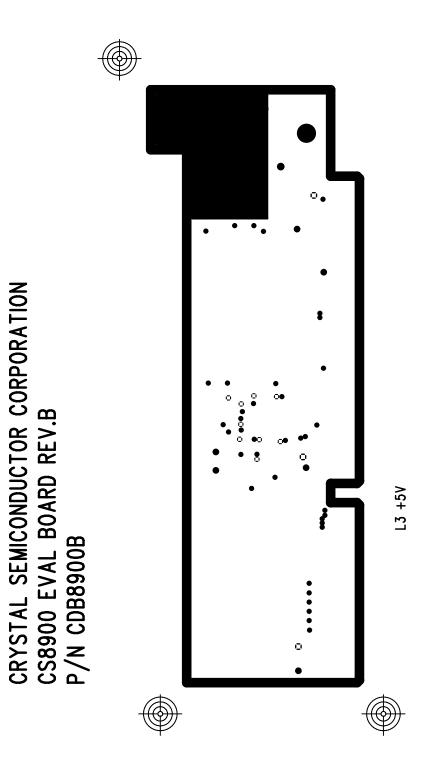

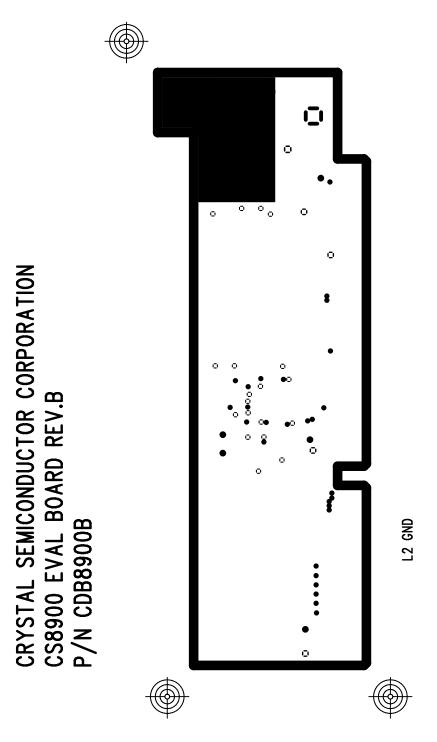

Figure 6. Placement of Components, Top Side

CIRRUS LOGIC®

Figure 7. Placement of Components, Solder Side

**CIRRUS LOGIC**®

PROM is not necessary for the CS8900A, and the CS8900A will respond to IO addresses 0300h through 030Fh after a reset.

Please refer to the CS8900A data sheet for information about programming the EEPROM. Please refer to "JUMPERLESS DESIGN" on page 45 of this document for information about EEPROM internal word assignments.

#### LEDs

Many embedded systems do not require LEDs for the Ethernet traffic. Therefore this reference design does not implement any LEDs. However, the CS8900A has direct drives for the three LEDs. Please refer to the data sheet for the CS8900A for a description of the LED functions available on the CS8900A.

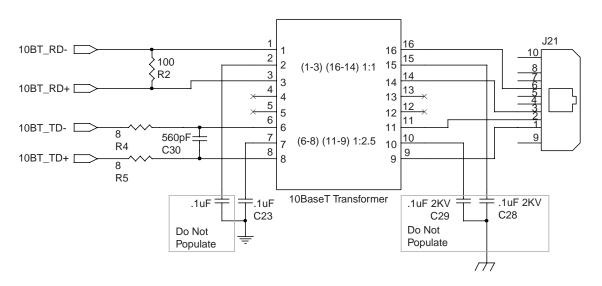

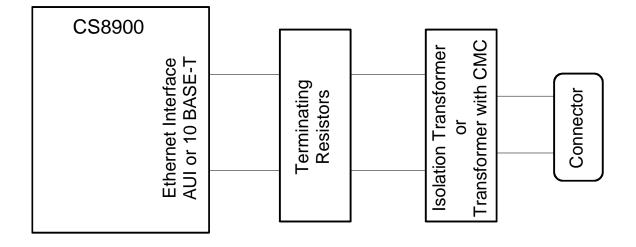

#### 10BASE-T Interface

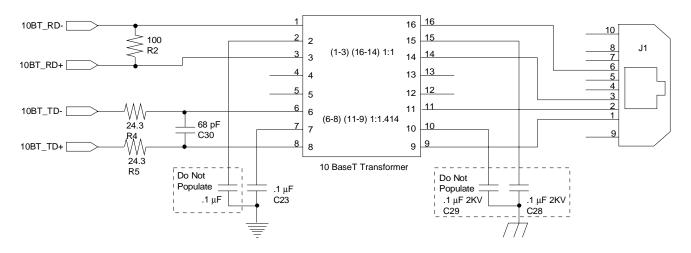

The 10BASE-T interface for the CS8900A is straight forward. Please refer to Figure 8 (3.3V) and Figure 10 (5V) for connections and components of this circuit. Transmit and receive signal lines from the CS8900A are connected to an isola-

tion transformer at location T1. This isolation transformer has a 1:1 ratio between the primary and the secondary windings on the receive side. It has a  $1:\sqrt{2}$  (1:1.414) ratio between the primary and the secondary windings for the transmit lines for 5V operation or a ratio of 1:2.5 for 3.3V operation. Resistor R1 provides termination for the receive lines. Resistors R2 and R3 are in series with the differential pair of transmit lines for impedance matching.

#### 10BASE-2 and AUI Interfaces

As many embedded systems require only a 10BASE-T interface, this reference design implements only the 10BASE-T interface. However, should a user require a 10BASE-2 or AUI interface, the CS8900A provides a direct interface to the AUI. Please refer to "Low Cost Ethernet Combo Card Reference Design: CRD8900" on page 21 of this document for details about the AUI interface.

#### Logic Schematics

Figures 8, 9 and 10 detail the logic schematics for the various circuits used in the reference design.

Figure 8. 10BASE-T Schematic 3.3V

Figure 9. Overall Schematic

Figure 10. 10BASE-T Schematic 5V

#### **Component Placement and Signal Routing**

Please refer to "Layout Considerations for the CS8900A" on page 35 of this document for more details on the placement of components on the board. It is important to provide very clean and adequate +5 V and ground connections to the CS8900A.

#### **Bill of Material**

Table 1 has a list components that are typically used to assemble this adapter card. For most of the components, there are several alternative manufacturers.

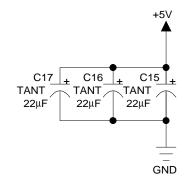

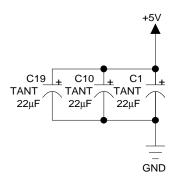

Figure 11. Decoupling Capacitors Schematic

| ltem | Reference #   | Description                       | Quantity | Vendor    | Part Number             |

|------|---------------|-----------------------------------|----------|-----------|-------------------------|

| 1    | C2, C5, C7C14 | Capacitor, 0.1 µF, X7R, SMT0805   | 10       |           |                         |

| 2    | C15, C16, C17 | Capacitor, 22 µF, SMT7343         | 3        |           |                         |

| 3    | R2, R3        | Resistor, 24.3, 1%, 1/8W, SMT0805 | 2        |           |                         |

| 4    | R1            | Resistor, 100, 1%, 1/8W, SMT0805  | 1        |           |                         |

| 5    | R4            | Resistor, 4.99K, 1%, SMT0805      | 1        |           |                         |

| 6*   | X1            | Crystal, 20.000 MHz               | 1        | M-tron    | ATS-49,20.000 MHz,18 pF |

| 7    | J1            | Connector, RJ45, 8 pin            | 1        | AMP       | 555164-1                |

| 8    | T1            | Transformer, 2, 1:1, 1:1.41       | 1        | Valor     | ST7011 (SOIC)           |

| 9    | U1            | ISA Ethernet Controller           | 1        | Crystal   | CS8900A                 |

| 10*  | U3            | 1K EEPROM                         | 1        | Microchip | 93C46 (8 pin SOIC)      |

\* Depending on system resources, these parts may not be needed.

Table 1. CS8900A Design Bill of Materials

#### LOW COST ETHERNET COMBO CARD REFERENCE DESIGN: CRD8900

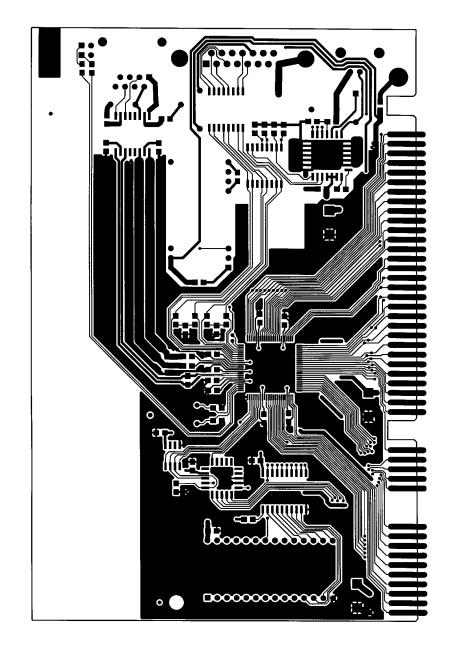

This section describes the hardware design of a lowcost, two-layer, full-featured Ethernet solution intended for use in PC ISA-bus. The goal of this design is a high degree of application flexibility. Therefore, a number of features (BootPROM, AUI, 10BASE-2) are supported. An example of this circuit is included in this Technical Reference Manual.

#### **General Description**

The CS8900A ISA Ethernet controller is used in this low cost, high performance ISA Ethernet adapter card. This card has AUI, 10BASE-T and 10BASE-2 interfaces. The very high level of integration of the CS8900A results in a very low component count. This makes it possible to design a half height, two layered 16 bit ISA Ethernet adapter card. Since the analog filters are integrated on the CS8900A, the card may be compliant with FCC part 15 class (B) compliant.

#### **Board Design**

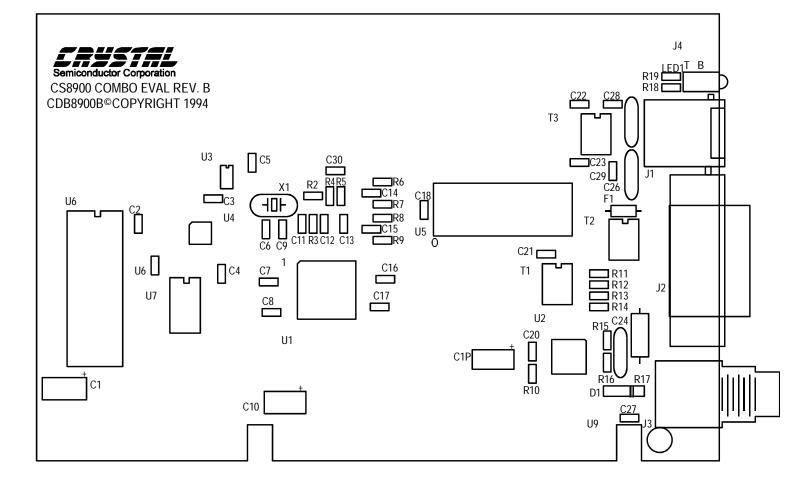

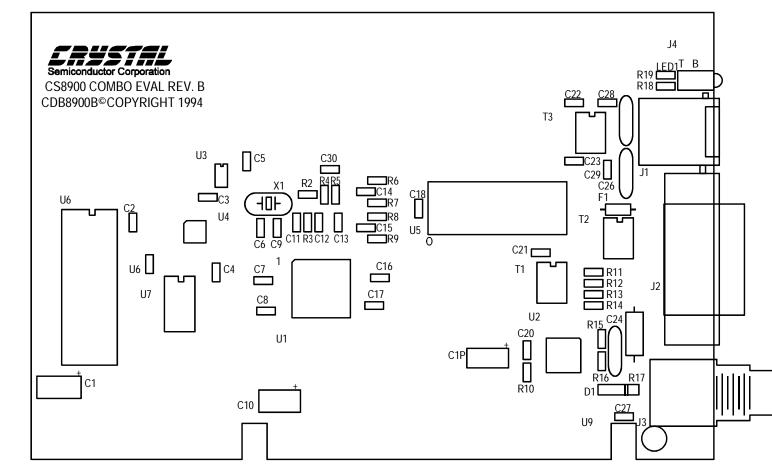

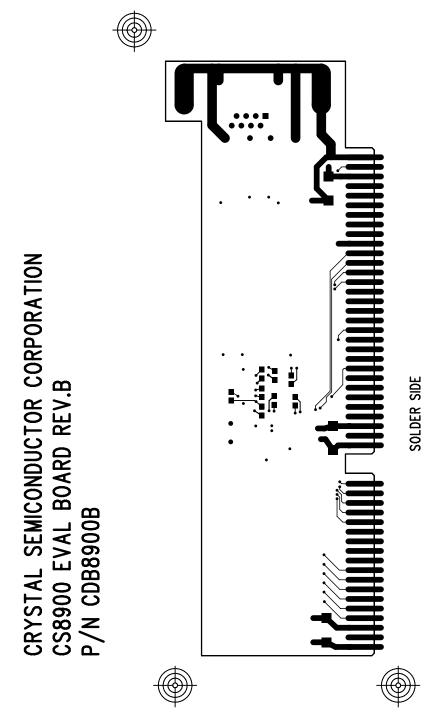

A recommended component placement is shown in Figure 12, and a recommended board schematics are shown in Figures 10 and 13 through 17.

#### Crystal Oscillator

The CS8900A, in the reference design, uses a 20.000 MHz crystal oscillator. Please note that the crystal must be placed very close to XTL1 and XTL2 pins of the CS8900A.

#### ISA Bus Interface

The ISA bus connections from the CS8900A can be easily routed to the ISA connector. If the pin-out of the CS8900A is placed as shown in Figure 12, there will be almost no cross-over of the ISA signals. It is also important to provide very clean and adequate +5 V and ground connections to the CS8900A.

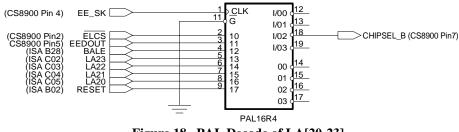

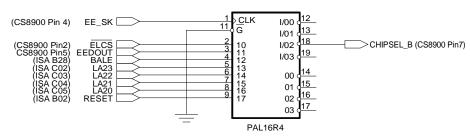

#### External Decode Logic

The CS8900A can be accessed in both I/O and memory modes. The CS8900A internally decodes the SA[0:19] address lines for the lower 1 M of memory. The reference design uses an external decode logic to allow the card to also decode decodes the upper 4 bits of the ISA address (LA[23:20]), thus allowing the CS8900A to reside anywhere in extended memory. This decode logic is implemented using a 16R4 PAL at location U4. This logic is configured by the CS8900A. The PAL then decodes the upper 4 bits of the ISA address. Please refer to "Addressing the CS8900A: I/O Mode, Memory Mode" on page 27 of this document for further information.

#### EEPROM

A 64 word (64 X16) EEPROM (location U3) is used in the reference design to interface with the CS8900A. This EEPROM holds the IEEE assigned Ethernet MAC (physical) address for the board. (see "Embedded Designs" on page 54) The EEPROM also holds other configuration information for the CS8900A. The last few bytes of the EEPROM are used to store information about the hardware configuration and software requirements.

Please refer to the CS8900A datasheet for information about programming the EEPROM. Please refer to "JUMPERLESS DESIGN" on page 45 of this document for information about EEPROM internal word assignment.

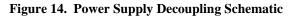

#### Socket for Optional Boot PROM

A socket is provided at location U6 for the optional Boot PROM. This Boot PROM is required in systems that require remote boot capability, for example diskless work stations. The 74LS245 data buffer at U7 is provided for the Boot PROM (See Figure 15). Inside the CS8900A there are registers that hold the Boot PROM base address (PacketPage base + 030h) and the Boot PROM address mask (PacketPage base + 034h). A 20 bit address

## CRYSTAL SEMICONDUCTOR CORPORATION CS8900 COMBO EVAL BOARD REV. B P/N CDB8900B

CIRRUS LOGIC

**AN83**

Figure 13. CS8900A Schematic (Combo Card Application)

**AN83**

Figure 15. Boot PROM Schematic

Figure 16. AUI Schematic

Figure 18. PAL Decode of LA[20-23]

loaded at the Boot PROM base address register indicates the starting location in host memory where the Boot PROM is mapped. The Boot PROM address mask indicates the size of the Boot PROM. The lower 12 bits of the mask are ignored and should be 000h. This limits the 434 Boot PROM size to increments of 4K bytes. The CS8900A will not generate an address decode for the Boot PROM until the Boot PROM base address register and the mask register are loaded. For example, say a 16K Boot PROM is used and it is to be located starting at address 0D0000h. Before this Boot PROM is accessed, load the following registers with the values shown in Table 2.

| Register Word<br>Offset<br>PacketPage<br>Base + | Hex<br>value | Description                           |

|-------------------------------------------------|--------------|---------------------------------------|

| 30h                                             | 0000h        | Boot PROM Base address -<br>low word  |

| 32h                                             | 000Dh        | Boot PROM Base address -<br>high word |

| 34h                                             | C000h        | Boot PROM address mask -<br>low word  |

| 36h                                             | 000Fh        | Boot PROM address mask -<br>high word |

Table 2. BootPROM Descriptions Stored in CS8900A

PacketPage

The address mask that will be used by the CS8900A is 0FC000h. The CS8900A will compare SA[19:14] with the value 0D0h. Whenever there is a match, it will assert the signal  $\overline{\text{CSOUT}}$  to generate an address decode for the Boot PROM. In the reference design, the same signal is also used to enable the data buffer, 74LS245, at location U7.

#### LEDs

A pair of LEDs are provided in the reference design to indicate link OK and line active status. The pair of LEDs are packaged one on the top of the other at location LED1. The top LED is driven by the  $\overline{\text{LIN-}}$  $\overline{\text{KLED}}$  pin while the bottom LED is driven by the  $\overline{\text{LANLED}}$  pin of the CS8900A. The top LED lights up when the CS8900A has the link pulse. The bottom LED lights up when the CS8900A transmits or receives a packet or senses a collision. The LEDs are directly driven by the CS8900A. Two 680 Ohm resistors limit the current flowing through the LED circuitry.

#### 10BASE-T Interface

The 10BASE-T interface for the CS8900A is straight forward. Please refer to Figure 8 or 10 for connections and components of this circuit. Transmit and receive signal lines from the CS8900A are connected to an isolation transformer at location T3. For 5V operation this isolation transformer has a 1:1 ratio between the primary and the secondary windings on the receive side and  $1:\sqrt{2}$  (1:1.41) ratio between the primary and secondary windings for the transmit lines. For 3.3V operation the receive side is 1:1 and the transmit side is 1:2.5. Resistor R2 provides termination for the receive lines. Resistors R4 and R5 are in series with the differential pair of transmit lines for impedance matching.

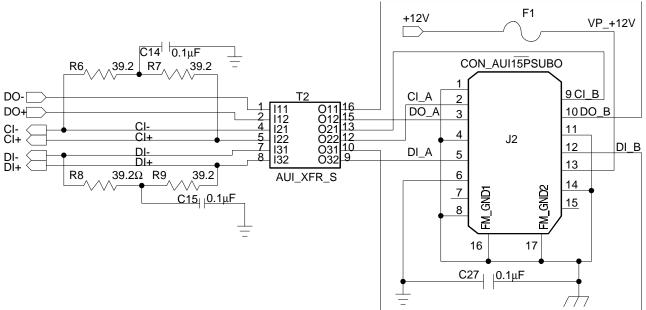

#### AUI Interface

Please refer to Figure 16 for connection of AUI signals to the CS8900A. The AUI lines from the 15pin sub-D connector (location J2) are connected to the CS8900A through an isolation transformer at T2. This isolation transformer has three windings for three pairs of differential AUI signals: transmit, receive and collision. All three windings have a turns ratio of 1:1 between the primary and secondary windings. Circuitry consisting of R6, R7 and C14 provides impedance termination for the collision differential pair. Circuitry consisting of R8, R9 and C15 provides impedance termination for the receive differential pair. The +12 volt power going out to the AUI connector is safeguarded by the fuse at F1. The AUI interface at J2 can be used to connect external Media Access Units (MAU). These MAUs allow the AUI interfaced to be used to interface with 10BASE-5 or 10BASE-F.

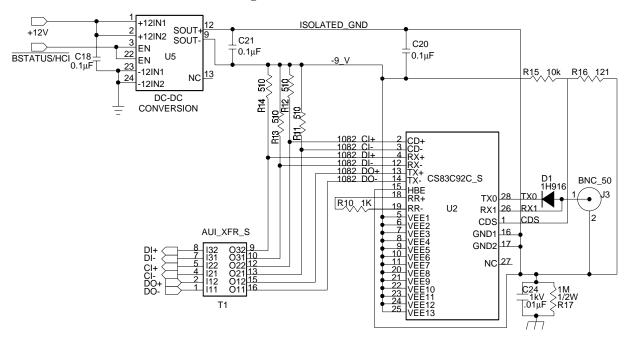

#### 10BASE-2 Interface

A 10BASE-2 transceiver IC, the 83C92C, is used to generate a 10BASE-2 interface for the reference design. Please refer to Figure 17 for details about the components and connection.

A 12 volt to -9 volt DC to DC voltage converter (location U5) is used to generate an isolated -9 volt supply for the 83C92C. The DC-DC converter used in the reference design has an enable pin. This enable pin is connected to the HC1 pin of the CS8900A. Usually the DC-DC converter is disabled when the 10BASE-2 interface is not used. This not only reduces power used by the adapter card but also eliminates any noise the 10BASE-2 circuitry can induce on the 10BASE-T or AUI interface that may be in use. This reference design uses a "low" enable DC-DC converter. That is, the DC-DC converter is enabled when the enable pin is logic low. However, the board can be built with a "high" enable DC-DC converter. In such a case, software that controls the enable and disable operations of the DC-DC converter should be modified.

An optional method is to use an integrated module that includes all the needed 10Base2 components. Contact Halo Electronics for information on their TnT integrated 10Base2 modules.

#### Logic Schematics

Figures 10 and 13 through 17 detail logic schematics for the various circuits used in the reference design.

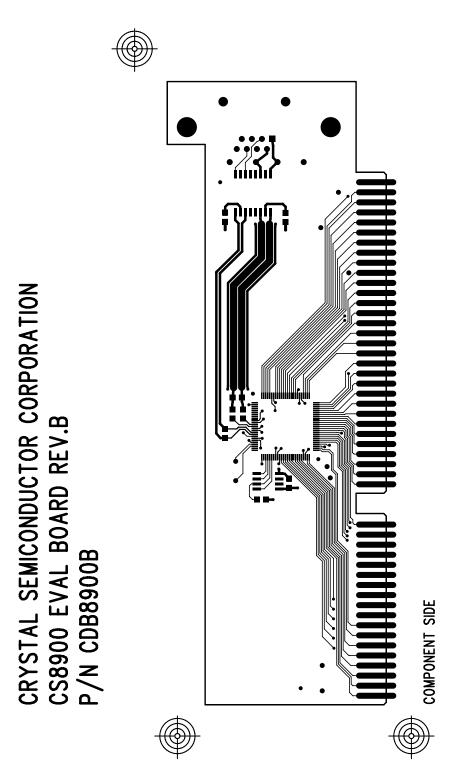

# Component Placement and Routing of Signals

Figure 12 shows the component placement used for the reference design. Figure 19 shows the routing of signals on the component side of the printed circuit board (PCB) while Figure 20 shows routing on the solder side. Please refer to "Layout Considerations for the CS8900A" on page 35 of this document for an explanation and information about placement of components on the board.

#### **Bill of Material**

Table 3 contains a list of components that are typically used to assemble this adapter card. For most of the components, there are several alternative manufacturers.

#### Addressing the CS8900A: I/O Mode, Memory Mode

The CS8900A, integrated Ethernet controller, has 20 address pins that directly connect to SA[19:0] of the ISA bus. The CS8900A has an internal address comparator to compare the ISA address with its base address registers.

#### I/O Mode

In IO mode, the lower 16 bits of the ISA address are compared with the address stored in IO Base Address register (Packet Page base + 020h). When an address match occurs and one of the IO command ( $\overline{IOR}$  or  $\overline{IOW}$ ) lines is active, the CS8900A responds to that IO access. The lower 4 bits of address lines are ignored by the address comparator. This dictates that the CS8900A must always be at a 16 byte address boundary of the ISA IO address space. The pin CHIPSEL is ignored for an IO mode access.

After RESET the CS8900A responds to IO address 0300h. However, this condition can be modified with use of an EEPROM or by software. Immediately after a reset, the CS8900A reads the EE-PROM interfaced to it. If the EEPROM has valid data (valid start data and correct checksum), it will read information stored in the EEPROM to initialize its own registers including the IO base address register. Please refer to the CS8900A datasheet for details about EEPROM configuration and programming. A CS8900A will always respond to valid IO address (even if its memory mode is enabled).

Figure 19. CRD8900 Top-Side Routing

Figure 20. CRD8900 Bottom Side Routing

| ltem  | Reference #                                      | Description                        | Quantity | Vendor                                        | Part Number    |

|-------|--------------------------------------------------|------------------------------------|----------|-----------------------------------------------|----------------|

| Base  | Configuration: I/O                               | Mode with 10BASE-T Interface       |          |                                               |                |

| 1     | C5, C7, C8,<br>C1113, C16, C17,<br>C22, C23, C27 | Capacitor, 0.1 μF, SMT0805, X7R    | 11       |                                               |                |

| 2     | C1, C10, C19                                     | Capacitor, 22 µF, SMT7343          | 3        |                                               |                |

| 3     | R3                                               | Resistor, 4.99K, 1%, SMT0805       | 1        |                                               |                |

| 4     | R18, R19                                         | Resistor, 681, 5%, 1/8W, SMT0805   | 2        |                                               |                |

| 5     | X1                                               | Crystal, 20.000MHz,18 pF           | 1        | M-tron                                        | ATS-49         |

| 6     | J4                                               | Board Bracket                      | 1        | Globe                                         | G436           |

| 7     | U1                                               | ISA Ethernet Controller            | 1        | Crystal                                       | CS8900A        |

| 8     | U3                                               | 1K EEPROM                          | 1        | Microchip                                     | 93C46          |

| 9     | R4, R5                                           | Resistor, 24.3, 1%, 1/8W, SMT0805  | 2        |                                               |                |

| 10    | R2                                               | Resistor, 100, 1%, 1/8W, SMT0805   | 1        |                                               |                |

| 11    | C30                                              | Capacitor, 68 pF, SMT0805          | 1        |                                               |                |

| 12    | Т3                                               | Transformer, 2, 1:1, 1:1.41        | 1        | Valor                                         | ST7010 (SOIC)  |

| 13    | J1                                               | Connector, RJ45, 8 pin             | 1        | AMP                                           | 555164-1       |

| Mem   | ory Mode Option                                  |                                    |          |                                               |                |

| 1     | C3                                               | Capacitor, 0.1 µF, SMT0805, X7R    | 1        |                                               |                |

| 2     | U4                                               | PAL                                | 1        | AMD                                           | PAL16R4B       |

| Boot  | PROM Options                                     |                                    |          |                                               |                |

| 1     | C2, C4                                           | Capacitor, 0.1 µF, SMT0805, X7R    | 2        |                                               |                |

| 2     | R1                                               | Resistor, 4.7K, 5%, 1/8W, SMT0805  | 1        |                                               |                |

| 3     | U6                                               | 32K X 8 EPROM Socket               | 1        |                                               |                |

| 4     | U7                                               | Octal Transceiver                  | 1        | TI                                            | 74LS245 (SOIC) |

| AUI ( | Option                                           |                                    |          | 1                                             |                |

| 1     | C14, C15                                         | Capacitor, 0.1 µF, SMT0805, X7R    | 2        |                                               |                |

| 2     | R6R9                                             | Resistor, 39.2, 1%, 1/8W, SMT0805  | 4        |                                               |                |

| 3     | F1                                               | Fuse, 1A                           | 1        |                                               |                |

| 4     | T2                                               | Transformer, 3, 1:1, 100 µH        | 1        | Valor                                         | ST7033 (SOIC)  |

| 5     | J2                                               | Connector, 15-pin sub-D            | 1        | AMP                                           | 745782-1       |

| 6     | J2                                               | AUI Slide Latch                    | 1        | AMP                                           | 745583-5       |

| 10BA  | SE2 Option                                       |                                    |          | •                                             | •              |

| 1     | C18, C20, C21                                    | Capacitor, 0.1 µF, SMT0805, X7R    | 3        |                                               |                |

| 2     | C24                                              | Capacitor, 0.01 µF, 1kV            | 1        | NIC Components                                | NCD103M1KVZ5U  |

| 3     | R11R14                                           | Resistor, 510, 1%, 1/8W, SMT0805   | 4        |                                               |                |

| 4     | R10                                              | Resistor, 1K, 1%, 1/8W, SMT0805    | 1        |                                               |                |

| 5     | R17                                              | Resistor, 1M, 10%, 1/2W, TH        | 1        |                                               |                |

| 6     | R15                                              | Resistor, 10K, 1%, 1/8W, SMT0805 1 |          |                                               |                |

| 7     | R16                                              | Resistor, 121, 1%, 1/8W, SMT0805 1 |          |                                               |                |

| 8     | D1                                               |                                    |          | 1N916                                         |                |

| 9     | T1                                               |                                    |          | ST7033 (SOIC)                                 |                |

| 10    | U2                                               | Ethernet Coax Transceiver          | 1        |                                               | 83C92C(PLCC)   |

| 11    | U5                                               | DC-DC Converter, 12V - 9V          | 1        | Valor                                         | PM7215         |

| 12    | J3                                               | Connector, BNC, 50 Ohm             | 1        | AMP                                           | 227161-7       |

|       | Option                                           |                                    | 1        | <b>۱</b> ــــــــــــــــــــــــــــــــــــ |                |

| 1     | LED1                                             | Bilevel LEDs                       | 1        | Ledtronics                                    | 21PCT110T4-G/Y |

|       |                                                  | able 3 CS8000A COMBO Card Refere   |          |                                               |                |

Table 3. CS8900A COMBO Card Reference Design Bill of Materials

**AN83**

#### Memory Mode

In the memory mode, there are two options where the CS8900A can be placed in the ISA memory address map, lower memory (below 1 Meg) or extended memory (above 1 Meg). The lower memory typically consists of the conventional memory (up to 640K) and upper memory (640K to 1 Meg. boundary). To access anything in extended memory, the processor (386 and above) is used in the "Enhanced Mode".

The CS8900A will respond to IO addresses programmed in its IO Base Address Register (Packet Page Base + 020h) even if memory mode is enabled. To enable memory mode, first write a proper 20 bit value to Memory Base Address register at Packet page base + 02Ch & 02Eh. Then set MemoryE (bit 0Ah) in the Bus CTL register (Register 17) to one.

These operations can be performed either by doing writes using IO mode accesses or using an EE-PROM as described in Sections 3.4 and 3.5 of the CS8900A datasheet. The CS8900A will respond to an ISA memory access, if the CHIPSEL pin is active (LOW), and the SA[19:0] match the value stored in Memory Base Address Registers. The lower 12 bits of the address lines are always ignored. This dictates that the CS8900A must always be placed at a 4K boundary in the ISA memory address space.

#### Lower Memory Mode

To use a CS8900A in the lower 1 Meg address space, <u>SMEMRD</u> and <u>SMEMWR</u> lines from the ISA bus are connected to <u>MEMR</u> and <u>MEMW</u> pins of CS8900A respectively. The <u>SMEMRD</u> and <u>SMEMWR</u> signals become active only for the lower 1 Meg of the ISA address space. The <u>CHIPSEL</u> pin of the CS8900A should be connected to ground.

#### Extended Memory Mode

The CS8900A can also be mapped in to the extended memory of a Personal Computer (PC) system. This provides flexibility and more options when several components are installed in a PC with CS8900A based network cards.

To address the CS8900A in extended memory mode, the processor is used in an enhanced mode. In an enhanced mode, 24 bits of ISA address lines are used for address generation. Since the CS8900A accepts 20 bits of address lines, an external address decoder circuit is required to decode the 4 upper address bits. The CS8900A has interface pins for external decoder circuit.

This arrangement makes provisions so that the CS8900A can be placed anywhere in the extended memory address map as long as it is at a 4K address boundary. The  $\overline{\text{MEMR}}$  and  $\overline{\text{MEMW}}$  signals of the ISA bus are active for any ISA memory space access, therefore, for extended memory mode operation, these signals are connected to the  $\overline{\text{MEMR}}$  and  $\overline{\text{MEMW}}$  pins of the CS8900A respectively.

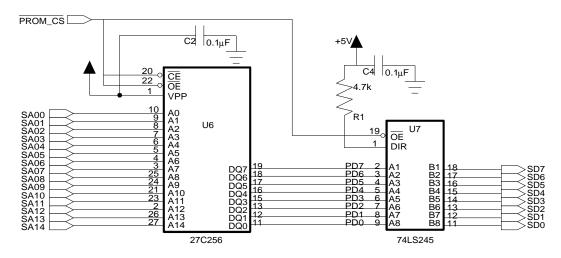

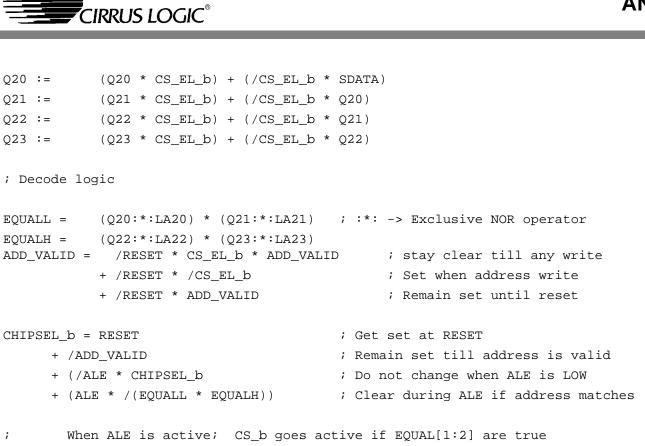

The external address decoder circuit consists of a single and simple Programmable Array Logic like a 16R4 or GAL16V8. Please refer to the schematic shown in Figure 21 as an example of such a decoder circuit. The PAL16R4 has 4 registers Q[23:20]. These registers are programmed by the serial input via the inputs EESK (clock), ELCS (enable pin) and EEDataOut (serial data out). This decoder compares the 4 upper address bits, namely LA[23:20], with the internal programmable register, Q[23:20]. Before memory mode of the CS8900A is enabled, Q[23:20] must be initialized to a proper value.

In the design example, Q[23:20] form a left shift register. The ELCS pin of the CS8900A is used inconjunction with EESK and EEDataOut pins to shift in the data for Q[23:20] serially. To program a value, set the ELSEL bit (bit A in Packet Page base + 040h) to HIGH. Then the EEPROM inter-

Figure 22. Typical CS8900A Ethernet Connection

face is used to generate the serial data stream on EEDataOut pin (serial data out) with the EESK (serial clock). Whenever ELSEL bit is set, ELCS pin becomes active (LOW) instead of EECS pin during the EEPROM operations. Since the EECS pin remains inactive, the EEPROM that is interfaced to the CS8900A is not enabled.

For the PAL in the design example, one should use a "Program disable" EEPROM command. (Opcode 00000b). For example, if the CS8900A is to be placed at PC memory space of 0A00000h, that means the Q[23:20] should be 0Ah. To program the 16R4, write 040Ah at Packet Page Base + 040h. The instruction will take about 10 micro-seconds to execute.

The electrical connections required to use external logic are shown in Figure 21. At reset, the

CS8900A samples  $\overline{\text{ELCS}}$  pin and if it is not "LOW", it realizes presence of external address decode logic. The same reset signal also makes ADD\_VALID inactive, and thus prevents a signal CHIPSEL\_b from becoming active until Q[23:20] are initialized. When a host CPU writes to PacketPage base address + 040h to program values for Q[23:20], the CS8900A then shifts that data serially in to the PAL or GAL. This makes ADD\_VALID signal active.

From this point onwards LA[23:20] are monitored whenever ALE is active (HIGH). When the decode logic finds a match, CHIPSEL\_b signal is asserted. This signal remains asserted until ALE becomes active and the LA[23:20] do not match with Q[23:20]. The internal decoder of the CS8900A is active only when CHIPSEL\_b is active (LOW).

Figure 21. PAL Decode of LA[20-23]

**AN83**

Figure 23 shows a simple PALASMTM program for the 16R4 PAL that is used in the design shown in Figure 21.

|                                             |       |       | escription         | Declaration Segment                                    |  |  |  |

|---------------------------------------------|-------|-------|--------------------|--------------------------------------------------------|--|--|--|

| TITLE High address decoder PATTERN          |       |       | oder PATTERN       |                                                        |  |  |  |

| REVIS                                       | ION   |       |                    |                                                        |  |  |  |

| AUTHOR Deva Bodas                           |       |       |                    |                                                        |  |  |  |

| COMPANY Cr                                  |       | Cryst | stal Semiconductor |                                                        |  |  |  |

| DATE 0                                      |       | 04/01 | /1994              |                                                        |  |  |  |

|                                             |       | _     |                    |                                                        |  |  |  |

| CHIP                                        | _deco | der   | PAL16R4            |                                                        |  |  |  |

| ;                                           |       |       |                    | PIN Declarations                                       |  |  |  |

| PIN                                         | 1     |       |                    | ; Serial clock from the CS8900A pin 4 (EESK)           |  |  |  |

| PIN                                         | 2     |       |                    | ; External Logic enable from the CS8900A pin 2 (ELCS*) |  |  |  |

| PIN                                         | 3     |       | SDATA              | ; Serial data in from the CS8900A pin 5 (EEDataOut)    |  |  |  |

| PIN                                         | 4     |       | ALE                | ; Address latch enable from the ISA bus                |  |  |  |

| PIN                                         | 5     |       | LA23               | ; Address 23                                           |  |  |  |

| PIN                                         | 6     |       | LA22               | ; Address 22                                           |  |  |  |

| PIN                                         | 7     |       | LA21               | ; Address 21                                           |  |  |  |

| PIN                                         | 8     |       | LA20               | ; Address 20                                           |  |  |  |

| PIN                                         | 9     |       | RESET              | ; ISA reset pin                                        |  |  |  |

| PIN                                         | 11    |       | OE                 | ; Output enable for the registered outputs             |  |  |  |

| PIN                                         | 12    |       | ADD_VALID          | COMB ; When high, Q[23:20] are programmed              |  |  |  |

| PIN                                         | 13    |       | EQUALH             | COMB ; Upper 2 bits of address match                   |  |  |  |

| PIN                                         | 19    |       | EQUALL             | COMB ; Lower 2 bits of address match                   |  |  |  |

| PIN                                         | 18    |       | CHIPSEL_b          | COMB ; CHIPSEL to the CS8900A pin 7                    |  |  |  |

| PIN                                         | 14    |       | Q20                | ; REG                                                  |  |  |  |

| PIN                                         | 15    |       | Q21                |                                                        |  |  |  |

| PIN                                         | 16    |       | ~                  | ; REG                                                  |  |  |  |

| PIN                                         | 17    |       | Q23                | ; REG                                                  |  |  |  |

| ; Boolean Equation Segment                  |       |       |                    |                                                        |  |  |  |

| EQUATIONS                                   |       |       |                    |                                                        |  |  |  |

| ; Serial shift register                     |       |       |                    |                                                        |  |  |  |

| ; When CS_EL_b is inactive (1), no change   |       |       |                    |                                                        |  |  |  |

| ; When CS_EL_b is active (0), shift in data |       |       |                    |                                                        |  |  |  |

|                                             |       |       |                    |                                                        |  |  |  |

; When ALE is inactive; previous state of CS\_b is latched.

Figure 23. PAL Program

**AN83**

#### Layout Considerations for the CS8900A

The CS8900A is a mixed signal device having digital and analog circuits for an Ethernet communication. While doing the PCB layout and signal connections, it is important to take the following precautions:

- Provide a low inductive path to reduce power and ground connection noise.

- Provide proper impedance matching especially to the Ethernet analog signals.

- Provide low inductive path, wider and short traces, for all analog signals.

It is important that a PCB designer follow suggestions made in this document for proper and reliable operation of the CS8900A. These guidelines will also benefit the design with good EMI test results.

#### General Guidelines

Figure 24 shows component placement for an ISA COMBO Ethernet adapter card using a CS8900A. The placement of the CS8900A should be such that the routes of the analog signals and the digital signals are not intermixing. No signal should route beneath the CS8900A on any plane.

#### **Power Supply Connections**

The CS8900A has 3 analog and 4 digital power pin pairs (Vcc and GND). Additional ground connections are provided. Each power pin pair should be connected to a 0.1  $\mu$ F bypass capacitor. Connect the extra ground pins directly the ground plane.

#### Two Layered Printed Circuit Board (PCB)

A two layered PCB has signal traces on the component and solder side of the PCB. Fill unused areas with copper planes. Typically, planes on the component side of the PCB are connected to ground and those on the solder side are connected to VCC or +5 volts.

Provide each pair of power pin with a  $0.1 \,\mu\text{F}$  bypass capacitor. Place each bypass capacitor as close as possible to the corresponding power pin pair. Con-

nect the capacitor to the pads of the power pins by short, wide traces, the other end of these traces should be connected to VCC and GND planes. Figure 19 and Figure 20 illustrate ground and power (Vcc) plane connections, respectively.

#### Multi-layered Printed Circuit Board

A multi-layered printed circuit board (PCB) typically has separate ground and power (Vcc) planes. Multi-layered PCBs are required when the component and trace density is high. Often discrete components like resistors and capacitors are placed on the solder side of a printed circuit board.

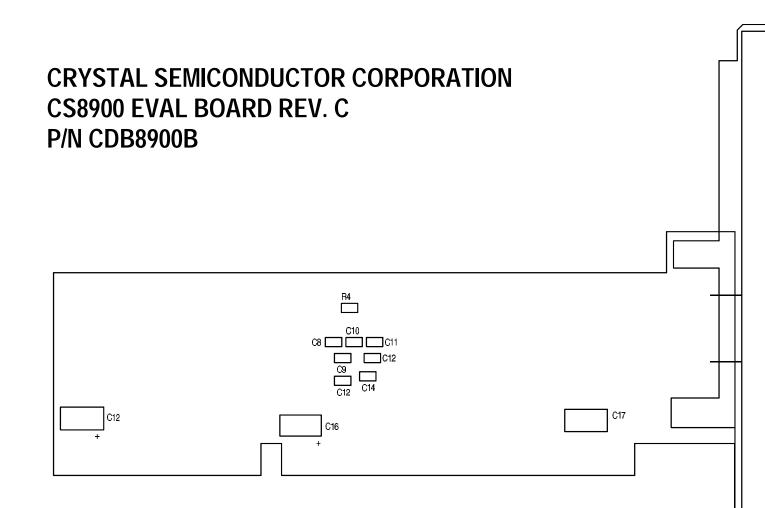

For a multi-layer PCB with all components on one side of the board, follow the power connection guide lines as explained in "Two Layered Printed Circuit Board (PCB)" on page 35. Instead of connecting the ground and Vcc to the copper fills on the component and solder side of the board, connect them to the internal ground and Vcc planes. Figures 27 through 30 show the four layers of the four-layer card.

For a multi-layered board the discrete components are to be placed on the solder side of the PCB, bypass capacitors for the CS8900A can be placed on the solder side of the PCB. Each bypass capacitor should be placed beneath the CS8900A and closest to its corresponding power pin pair. Figures 31 and 32 illustrate the placement and routing of one bypass capacitor.

#### Routing of the Digital Signals

Most of the digital signals from the CS8900A go to the ISA bus connector. Route these signals directly to the connector. Isolate the digital signals from analog signals.

#### Routing of the Analog Signals

Routing of the clock signals: Place the 20.000 MHz crystal within one inch of XTL1 (pin #97) and XTL2 (pin #98) pins of the CS8900A.

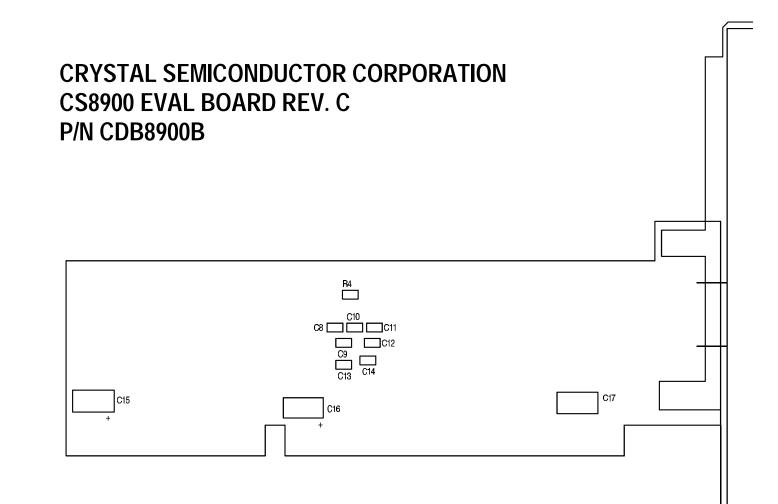

## CRYSTAL SEMICONDUCTOR CORPORATION CS8900 COMBO EVAL BOARD REV. B P/N CDB8900B

Figure 24. General placement on an ISA adapter card

**AN83**

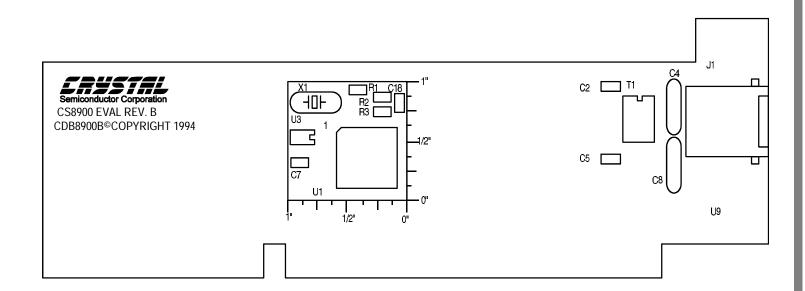

# CRYSTAL SEMICONDUCTOR CORPORATION CS8900 EVAL BOARD REV. B P/N CDB8900B

Figure 25. Placement of Components, Top Side

**CIRRUS LOGIC**®

**AN83**

**CIRRUS LOGIC**®

Figure 27. Component (top) side of four-layer board

Figure 28. +5V Plane of four-layer board

Figure 29. Ground Plane of four-layer board

Figure 30. Solder side (bottom) of four-layer board

Figure 31. Placement of Decoupling Capacitor (Bottom side, under CS8900A)

Figure 32. Routing of Decoupling Capacitor (Top side, component side)

The 20.000 MHz crystal traces should be short, have no via, and run on the component side.

Biasing resistor at RES pin of the CS8900A: A 4.99 K $\Omega$  resistor is connected between pins RES (pin #93) and AVSS3 (pin #94) of the CS8900A. This resistor biases internal analog circuits of the CS8900A, and should be placed as close as possible to RES pin (pin #93) of the CS8900A.

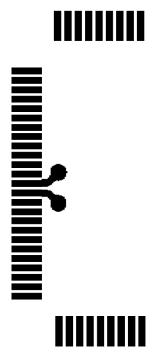

Routing of the 10BASE-T signals: Four signals are used for 10BASE-T communication, two dif-

ferential transmit signals and two differential receive signals. An isolation transformer is placed between the transmit and receive traces and a RJ-45 (modular phone jack) connector. The isolation transformer should be placed as close as possible to the RJ-45 connector. Both transmit and receive signal traces should be routed so they are parallel and of equal length. The signal traces should be on the component side and should have direct and short paths. The widths of the receive signal traces should at least be 25 mil. while widths of the trans-

mit signal traces should be at least 100 mil. This will provide a good impedance matching for the transmit and receive circuitry inside the CS8900A. A ground trace should be run parallel to the transmit traces. Also, a ground plane should run underneath the transmit and receive traces on the solder side of a two layered PCB. Please refer to the Figures 33 and 34 for illustration of the above guide lines.